## Frequency Translation Techniques for Interference-Robust Software-Defined Radio Receivers

## Invitation

On Thursday,

November 12th 2009

at 16:45

in Collegezaal 2

of the Spiegel building,

I will be defending

my thesis.

Frequency Translation

Techniques for

Interference-Robust

Software-Defined

Radio Receivers

At 16:30, I will give a short introduction to my thesis.

You are most welcome to attend the introduction, the defense, and the reception afterwards.

Zhiyu Ru

Zhiyu Ru

# FREQUENCY TRANSLATION TECHNIQUES FOR INTERFERENCE-ROBUST SOFTWARE-DEFINED RADIO RECEIVERS

Title: Frequency Translation Techniques for Interference-Robust

Software-Defined Radio Receivers

Author: Zhiyu Ru

ISBN: 978-90-365-2925-9

Copyright  $\ @$  2009 by Zhiyu Ru

All rights reserved. Reproduction in whole or in part is prohibited without the prior written permission of the copyright owner.

PRINTED IN THE NETHERLANDS

## FREQUENCY TRANSLATION TECHNIQUES FOR INTERFERENCE-ROBUST SOFTWARE-DEFINED RADIO RECEIVERS

#### **DISSERTATION**

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Thursday 12 November 2009 at 16:45

by

Zhiyu Ru

born on 8 February 1981 in Nanjing, China

### This dissertation is approved by

the promotor, prof.dr.ir. Bram Nauta

and the assistant promotor, dr.ing. Eric A. M. Klumperink

#### Committee:

Chairman:

prof.dr.ir. J.H.A. de Smit Universiteit Twente

Secretary:

prof.dr.ir. A.J. Mouthaan Universiteit Twente

Promotor:

prof.dr.ir. B. Nauta Universiteit Twente

**Assistant Promotor:**

dr.ing. E.A.M. Klumperink Universiteit Twente

Members:

prof.dr. J.R. Long Technische Universiteit Delft prof.dr.ir. M. Steyaert Katholieke Universiteit Leuven

prof.dr.ir. C.H. Slump Universiteit Twente prof.ir. A.J.M. van Tuijl Universiteit Twente

#### Abstract

There has been a growing demand for wireless communications and diverse communication standards have been developed over time, e.g. GSM, Bluetooth, Wi-Fi, etc. For convenience of use, people desire a universal radio to be able to communicate anywhere using any standard. A software-defined radio (SDR) which aims at greater programmability can meet such a demand. However, there are a number of technical challenges to make a SDR receiver practical.

This thesis focuses on frequency translation (FT) techniques and addresses two key SDR challenges: the robustness to out-of-band interference (OBI) and the compatibility with CMOS scaling and system-on-chip (SoC) integration. The thesis studies the principles and the performance limitations of existing FT techniques and proposes new circuit-and-system techniques to improve SDR receivers.

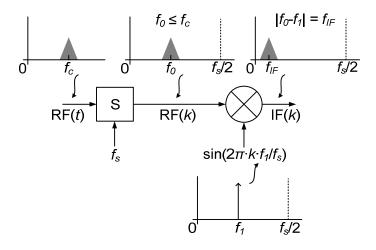

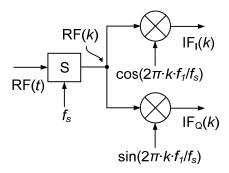

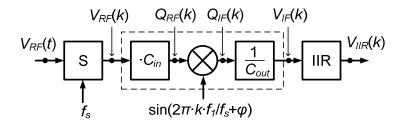

Fundamental differences between various FT techniques are highlighted by means of a classification and comparison of mixing and sampling. This leads to the definition of a new discrete-time (DT) mixing technique. The suitability of RF-mixing and RF-sampling receivers to SDR is evaluated. RF sampling seems to be more compatible with CMOS scaling and SoC integration. However, existing RF-sampling techniques are narrowband and are not directly suitable for a wideband SDR receiver.

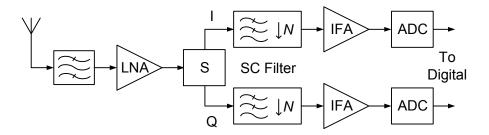

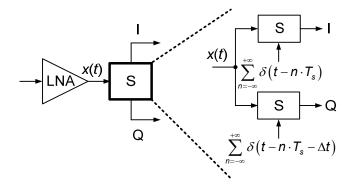

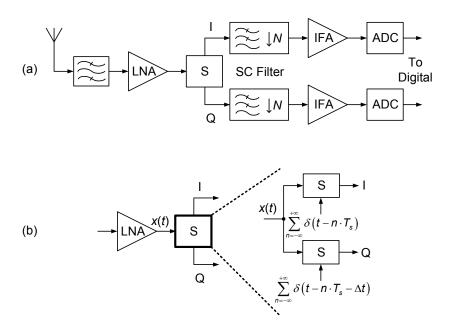

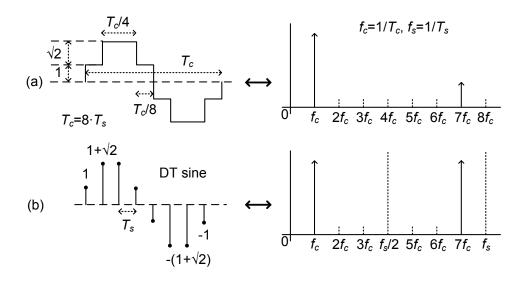

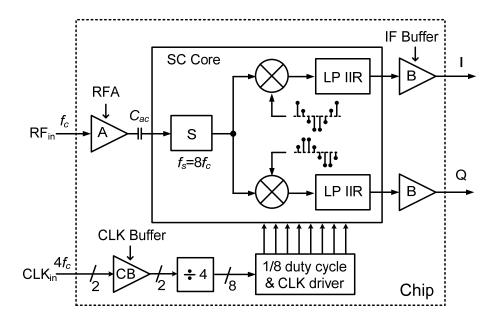

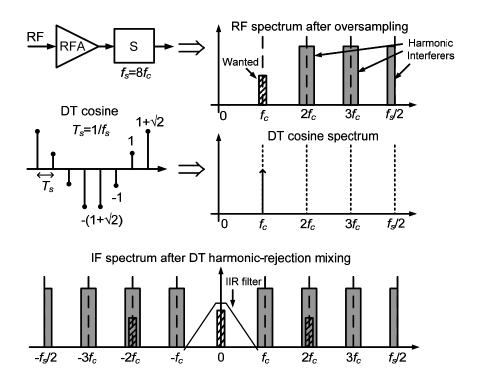

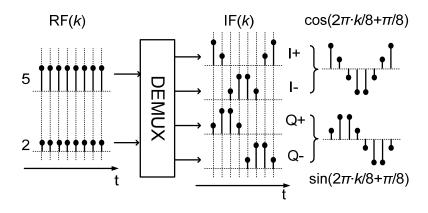

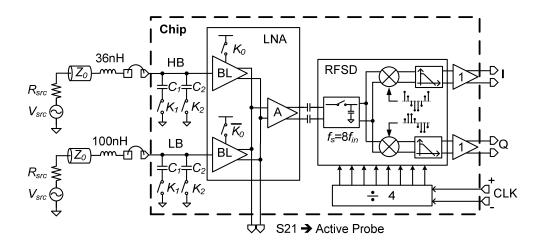

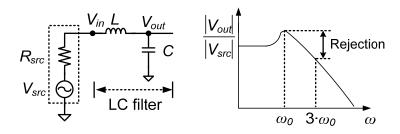

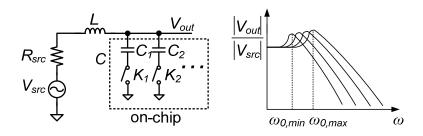

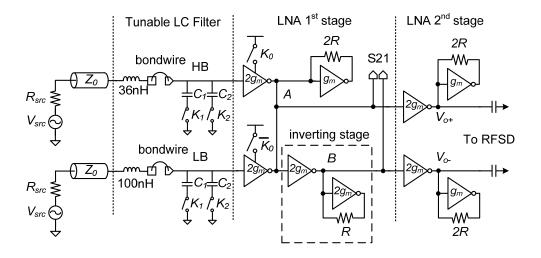

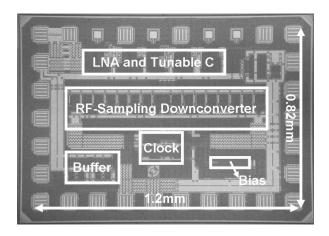

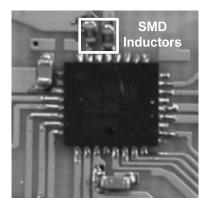

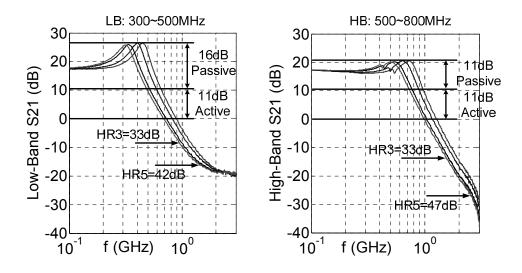

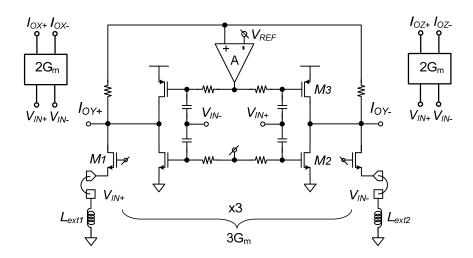

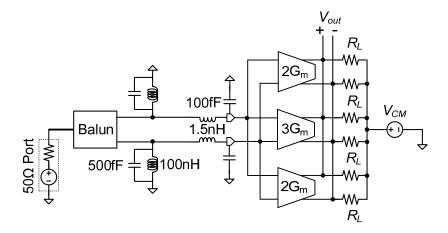

To address this issue, a DT-mixing technique is proposed which performs a mixing operation in the DT domain after RF sampling. It can make RF sampling more suitable to wideband SDR receivers because it has two properties: wideband phase shifting and wideband harmonic rejection (HR). DT mixing can be realized using de-multiplexing of samples. To verify the concept, a 200-to-900MHz DT-mixing downconverter with 8-times oversampling and 2<sup>nd</sup>-to-6<sup>th</sup> HR is implemented in 65nm CMOS. To construct a complete RF-sampling receiver, a tunable LC filter and a linearized low-noise amplifier (LNA) are applied as pre-stages of the DT-

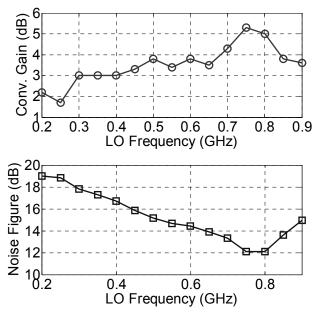

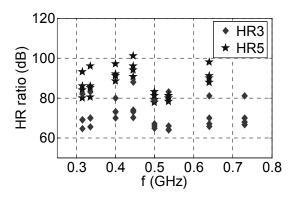

mixing downconverter. The LC filter employs an external coil and on-chip switchable capacitors. The LNA employs cascaded inverter stages linearized via an enhanced voltage mirror. The RF-sampling receiver achieves a minimum NF as low as 0.8dB and improves HR by 30dB compared to the downconverter alone.

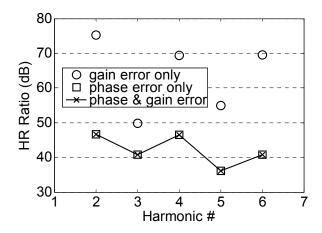

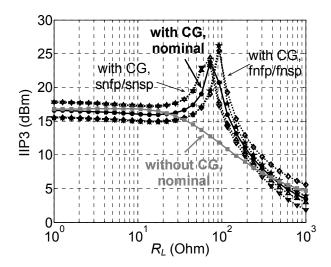

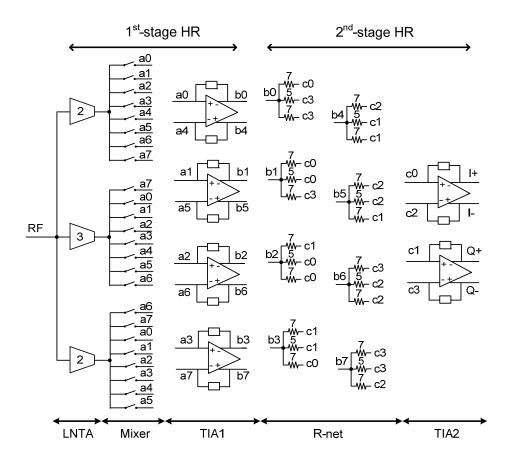

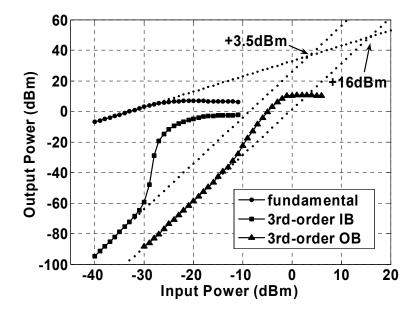

To be more robust to OBI, two FT techniques are proposed: one to improve the out-of-band linearity and the other to make the HR robust to mismatch. A low-pass blocker filtering technique is proposed to avoid voltage gain at radio frequencies (RF) but make voltage gain only at baseband simultaneously with low-pass filtering to attenuate OBI. The low voltage gain at RF is realized by means of a low "mix-impedance", which is analyzed quantitatively. A 2-stage polyphase HR technique is proposed to perform HR in cascaded stages to dramatically improve the amplitude accuracy. To also achieve the high phase accuracy, a simple and accurate frequency divider is presented. The effects of random amplitude and phase errors to HR are analyzed. To demonstrate these concepts, a 65nm CMOS receiver based on RF mixing shows +3.5dBm in-band IIP3 and +16dBm out-of-band IIP3. More than 60dB HR ratio is measured over 40 randomly-selected chips. The multiphase clock generator works up to 0.9GHz while the -3dB RF bandwidth is measured up to 6GHz.

## **Contents**

| Al | Abstract                                                             |    |  |

|----|----------------------------------------------------------------------|----|--|

| 1  | Introduction                                                         | 1  |  |

|    | 1.1 Software(-Defined) Radio: Motivation and Origins                 | 1  |  |

|    | 1.2 Challenges                                                       | 5  |  |

|    | 1.3 State of the Art                                                 | 12 |  |

|    | 1.3.1 Wideband Receivers                                             | 13 |  |

|    | 1.3.2 Robustness to Out-of-Band Interference                         | 16 |  |

|    | 1.3.3 Flexible Baseband Channel Selection                            | 20 |  |

|    | 1.3.4 Compatibility with CMOS Scaling and SoC Integration            | 21 |  |

|    | 1.4 Research Objectives                                              | 21 |  |

|    | 1.5 Thesis Organization                                              | 22 |  |

|    | 1.6 References                                                       | 24 |  |

| 2  | Frequency Translation Fundamentals                                   | 29 |  |

|    | 2.1 Why Frequency Translation                                        | 30 |  |

|    | 2.2 Classification of Downconversion Techniques                      | 33 |  |

|    | 2.3 Fundamental Distinctions between Mixing and Sampling Principles. | 35 |  |

|    | 2.3.1 Time Domain: Information Rate Changes or Not?                  | 35 |  |

|    | 2.3.2 Frequency Domain: Frequency Translation Happens or Not?        | 36 |  |

|    | 2.4 Receiver Architectures for SDR                                   | 38 |  |

|    | 2.4.1 Receiver Architectures                                         | 39 |  |

|    | 2.4.2 Suitability to SDR                                             | 40 |  |

|   | 2.5 Challenges of RF Sampling for Wideband Receivers         | 45  |

|---|--------------------------------------------------------------|-----|

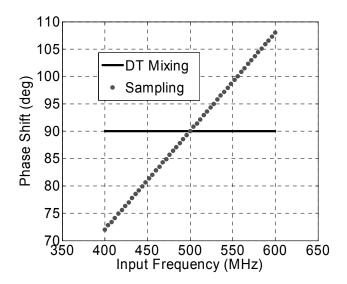

|   | 2.5.1 Frequency-Dependent Phase Shift.                       | 46  |

|   | 2.5.2 Aliasing of Noise and Interference                     | 50  |

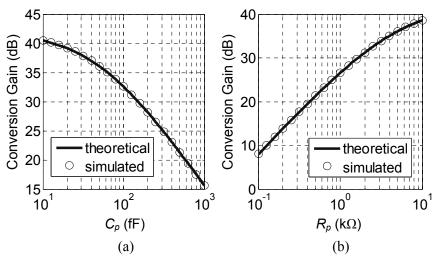

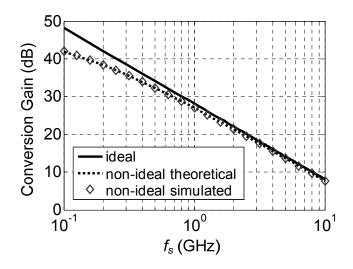

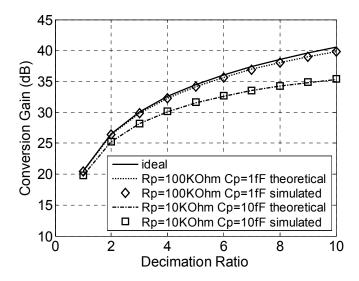

|   | 2.5.3 Frequency-Dependent Conversion Gain of Charge Sampling | 52  |

|   | 2.6 Conclusions                                              | 65  |

|   | 2.7 References                                               | 67  |

| 3 | Discrete-Time Mixing Receiver for RF-Sampling SDR            | 71  |

|   | 3.1 Introduction                                             | 71  |

|   | 3.2 Discrete-Time Mixing Receiver Concept                    | 72  |

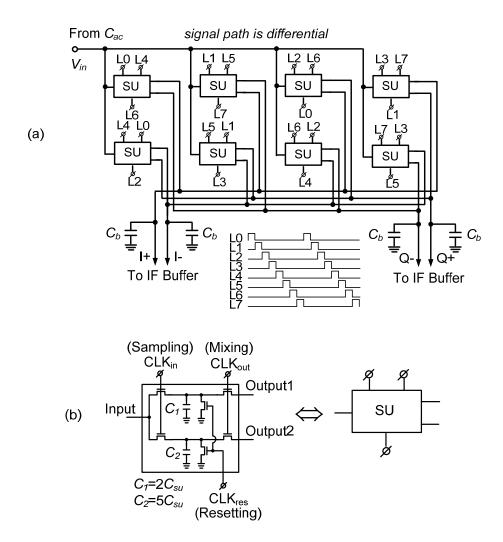

|   | 3.2.1 Wideband Quadrature Demodulation                       | 73  |

|   | 3.2.2 Wideband Harmonic Rejection.                           | 76  |

|   | 3.3 Proof-of-Concept Implementation.                         | 78  |

|   | 3.3.1 Receiver Architecture                                  | 79  |

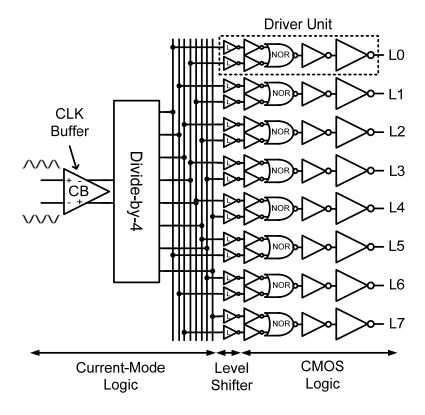

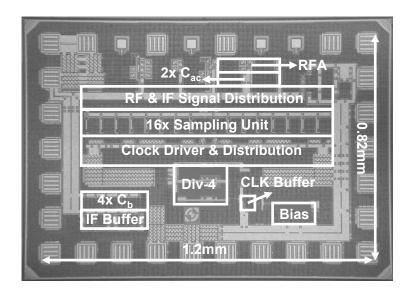

|   | 3.3.2 Circuit Implementation                                 | 81  |

|   | 3.4 Experimental Results                                     | 90  |

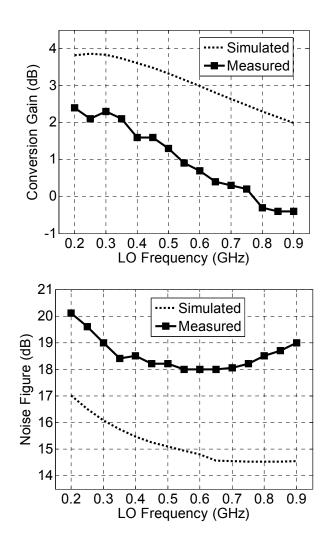

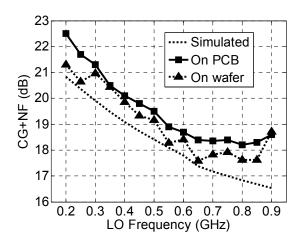

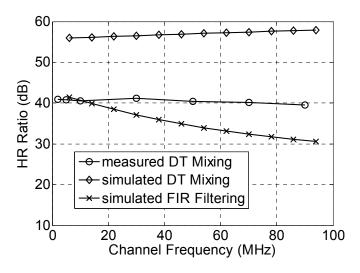

|   | 3.4.1 Conversion Gain and Noise Figure.                      | 90  |

|   | 3.4.2 Harmonic Rejection.                                    | 94  |

|   | 3.4.3 Performance Summary                                    | 96  |

|   | 3.5 Conclusions                                              | 98  |

|   | 3.6 References                                               | 98  |

| 4 | Filter and Amplifier Techniques for Interference Robustness  | 101 |

|   | 4.1 Introduction                                             | 101 |

|   | 4.2 RF-Sampling Receiver Architecture                        | 104 |

|   | 4.3 Digitally-Controlled LC Filter                           | 105 |

|   | 4.3.1 Filter Concept                                         | 105 |

|   | 4.3.2 Implementation                                         | 109 |

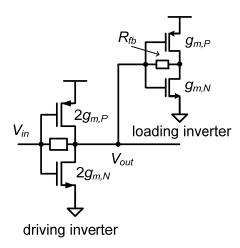

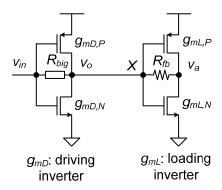

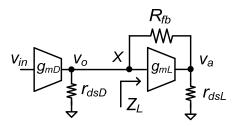

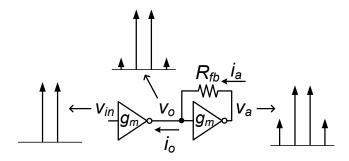

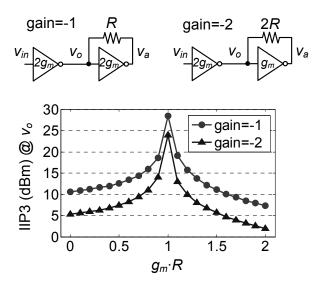

|   | 4.4 Amplifier based on Enhanced Voltage Mirror               | 113 |

|   | 4.4.1 LNA Topology                                           | 113 |

|   | 4.4.2 Mechanism of Nonlinearity Compensation                 | 117 |

|   | 4.5 Experimental Results                                     | 120 |

|---|--------------------------------------------------------------|-----|

|   | 4.5.1 Filter Response, Gain, NF and HR                       | 121 |

|   | 4.5.2 Linearity                                              | 124 |

|   | 4.6 Conclusions                                              | 126 |

|   | 4.7 References                                               | 127 |

| 5 | Downconversion Techniques Robust to Out-of-Band Interference | 129 |

|   | 5.1 Introduction                                             | 130 |

|   | 5.2 Low-Pass Blocker Filtering.                              | 131 |

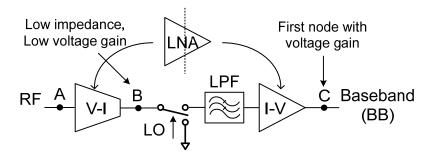

|   | 5.2.1 Concept                                                |     |

|   | 5.2.2 Realization.                                           |     |

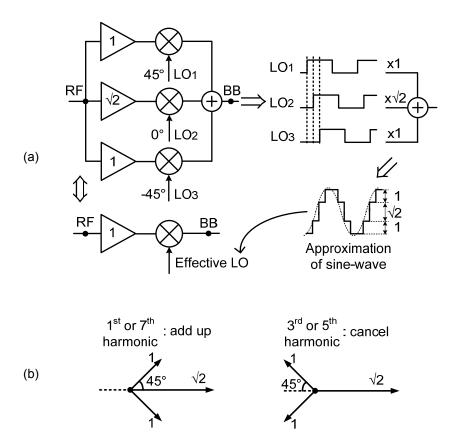

|   | 5.3 2-stage Polyphase Harmonic Rejection                     | 136 |

|   | 5.3.1 Block Diagram                                          | 137 |

|   | 5.3.2 Working Principle                                      | 138 |

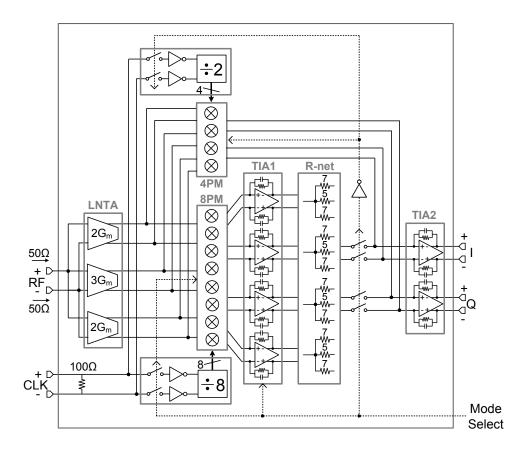

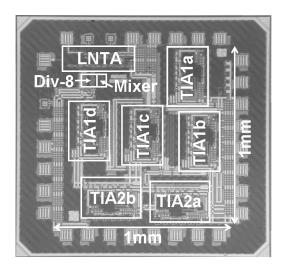

|   | 5.4 Chip Implementation                                      | 142 |

|   | 5.4.1 Linear LNTA                                            | 143 |

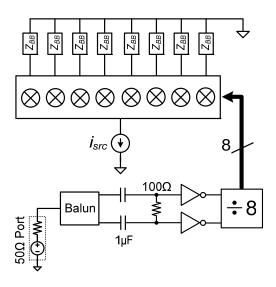

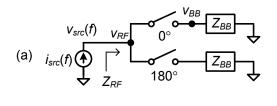

|   | 5.4.2 Passive Mixer                                          | 146 |

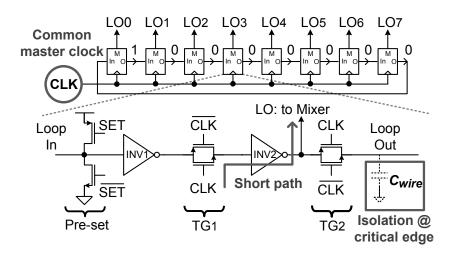

|   | 5.4.3 Accurate Multiphase Clock                              | 147 |

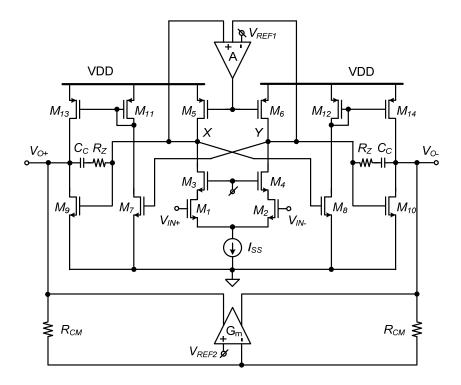

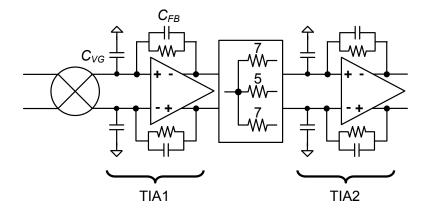

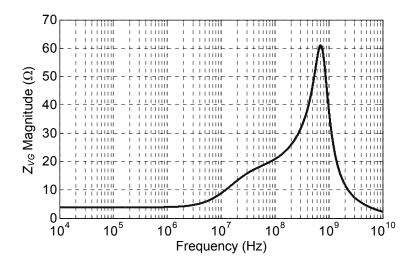

|   | 5.4.4 High-Swing TIA                                         | 151 |

|   | 5.4.5 Baseband R-net.                                        | 154 |

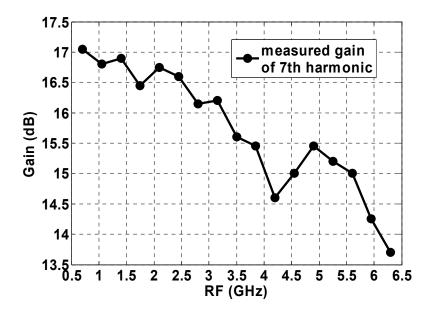

|   | 5.5 Receiver Frequency Range Extension                       | 154 |

|   | 5.6 Experimental Results.                                    | 157 |

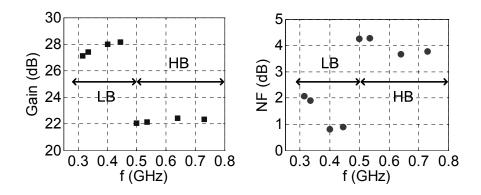

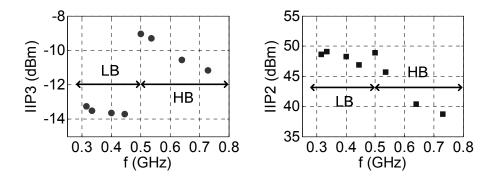

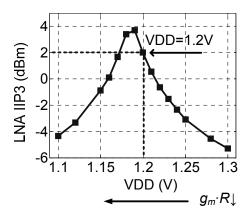

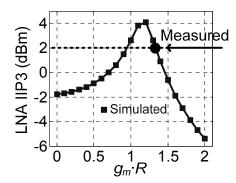

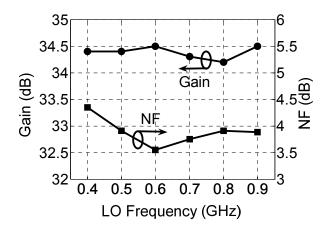

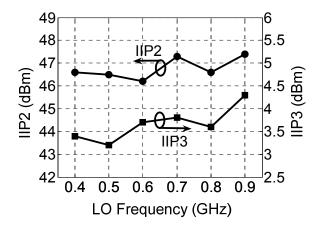

|   | 5.6.1 Gain, NF, in-band IIP2/IIP3, and RF bandwidth          | 158 |

|   | 5.6.2 Out-of-Band IIP2/IIP3                                  | 160 |

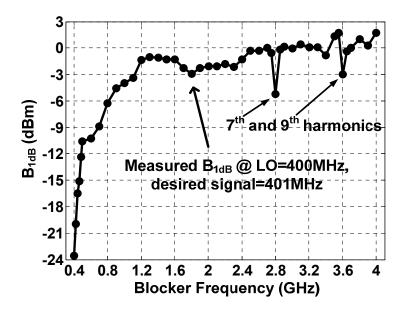

|   | 5.6.3 1dB Compression Point and Blocker Filtering            | 161 |

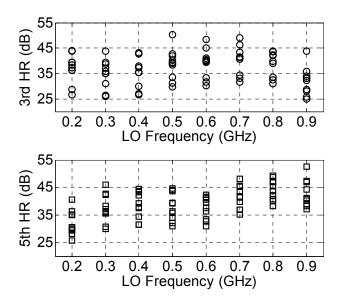

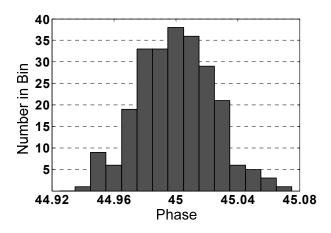

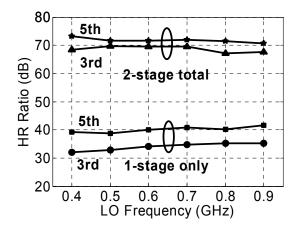

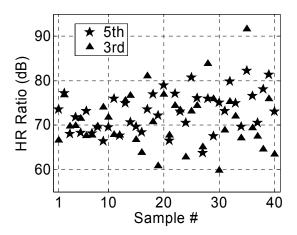

|   | 5.6.4 Harmonic Rejection                                     | 163 |

|   | 5.6.5 Performance Summary and Benchmark                      | 165 |

|   | 5.7 Conclusions.                                             | 167 |

|   | 5.8 References                                               | 168 |

| 6                   | Conclusions 1 |                                                    |                  |  |  |

|---------------------|---------------|----------------------------------------------------|------------------|--|--|

|                     | 6.1           | Summary and Conclusions.                           | 171              |  |  |

|                     | 6.2           | Original Contributions.                            | 176              |  |  |

|                     | 6.3           | Future Work                                        | 179              |  |  |

|                     | 6.4           | References                                         | 181              |  |  |

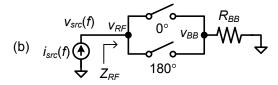

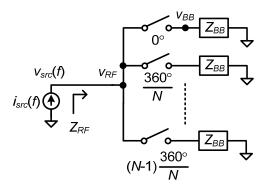

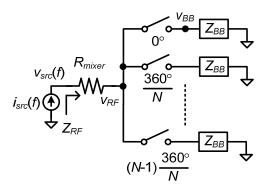

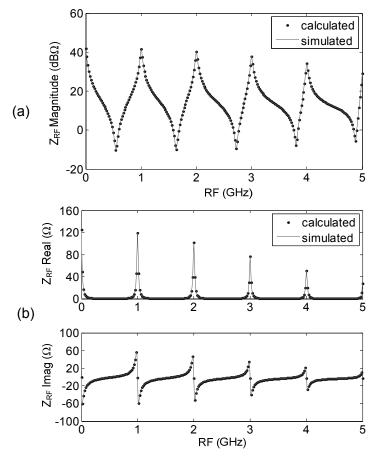

| A                   | Ana           | alysis of the "Mix-Impedance"                      | 183              |  |  |

|                     | A.1           | Derivation                                         | 183              |  |  |

|                     |               | A.1.1 Impedance without Spectrum Shift             | 185              |  |  |

|                     |               | A.1.2 Impedance with Spectrum Shift                | 188              |  |  |

|                     | A.2           | Simulation                                         | 190              |  |  |

|                     | A.3           | References                                         | 195              |  |  |

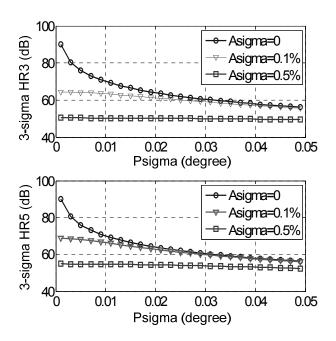

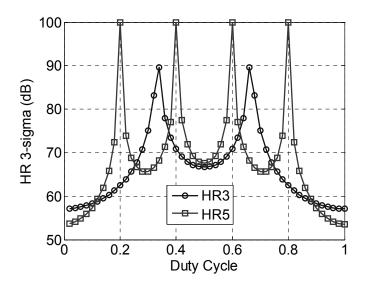

| В                   | Effe          | ect of Random Amplitude and Phase Errors to Harmon | ic Rejection 197 |  |  |

|                     | B.1           | Derivation                                         | 197              |  |  |

|                     | B.2           | Simulation                                         | 199              |  |  |

|                     | B.3           | References                                         | 201              |  |  |

| Acknowledgements 20 |               |                                                    |                  |  |  |

| Samenvatting        |               |                                                    |                  |  |  |

| Pu                  | Publications  |                                                    |                  |  |  |

| About the Author    |               |                                                    |                  |  |  |

### Chapter 1

#### Introduction

Wireless communications rely on radio. Future wireless communications rely on software-defined radio (SDR), which makes radio more flexible. However, a low-cost practical SDR still stays as a concept so far. This thesis addresses the main challenges of realizing practical SDR receivers, focusing on the analog front-end.

Section 1.1 describes the motivation behind the trend towards SDR and the actual origins of the concept of software radio and software-defined radio. From the concept to a practical SDR, a few major challenges exist. Section 1.2 discusses these challenges and Section 1.3 reviews the up-to-date solutions. After that, Section 1.4 defines the objectives of this work. Then Section 1.5 gives an overview on the organization of this thesis. Section 1.6 provides the references of the chapter.

#### 1.1 Software(-Defined) Radio: Motivation and Origins

Communication is essential for people, and the modern society heavily relies on it. Assisted by wireless technologies, people can communicate over long distances, flexibly at different places, and even while moving. Today, radio communication not just exists but it is everywhere and keeps growing. As a typical example, by 2008, the global mobile phone penetration rate was already more than 50% and it is predicted to reach 75% by 2011 [1].

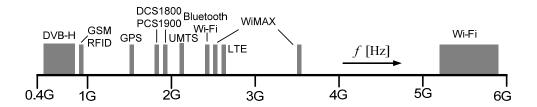

In the mean time, different communication standards have been developed to serve various applications in our daily life. To give a couple of examples, in the spectrum of 400MHz to 6GHz (Fig. 1.1) which is typically used for mobile applications, we

Figure 1.1 An example of spectrum allocation for mobile communications

have the cellular standards GSM, UMTS, and LTE, the wireless networking standards Wi-Fi and WiMAX, the mobile TV standard DVB-H, the navigation standard GPS, and the short-range communication standards Bluetooth and RFID, etc. The list is only getting longer as new standards are still emerging.

For convenience of use, it is a natural step to combine as many applications as possible into a single mobile radio device, i.e. to add more functionality. Compared to the approach of adding separate radio hardware for every application, the use of flexible hardware controlled by software can make the device smaller, lighter, more flexible, and at lower cost. This trend of *radio evolution*, i.e. moving functionality into software for a *flexible* multi-function radio device, leads to the emerging of the term "software radio" (SWR), coined in the early 90's by Mitola [2] [3]. Similar trends can be seen in many other electronic systems.

With radio functions mainly implemented in software, SWR refers to a universal radio platform being able to cope with *current and future* communication standards only by running and upgrading different software. The goal of SWR is to make a radio as flexible as a computer: the software defines the application.

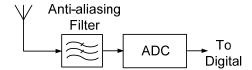

However, a SWR receiver has to first convert an analog radio signal into a digital representation before the signal can be handled by software. Consequently, an analog-to-digital converter (ADC) is indispensible. As shown in Fig. 1.2, an *ideal* SWR receiver [4] [5] moves the ADC towards the antenna, through an anti-aliasing filter. Such a radio concept can be very flexible because it minimizes the analog hardware and maximizes the usage of digital hardware which provides the platform to run software.

Figure 1.2 Ideal software-radio (SWR) receiver but impractical yet

The dominant technology for digital circuits is CMOS which stands for Complementary Metal-Oxide Semiconductor. Moreover, commercially it is attractive to achieve a high level of integration for a low cost, and the trend is clear: system-on-chip (SoC), with both analog and digital implemented on the same chip. Therefore, SWR hardware is preferably implemented in CMOS.

As mentioned, an ideal SWR receiver requires a high-performance ADC to directly digitize RF signal. However, without downconversion and filtering ahead, the required ADC performance such as speed and dynamic range is usually impractical in CMOS. For example, assuming at least 10GS/s speed and 16-bit resolution are required to receive RF signals up to 5GHz, and assuming 1pJ/conversion for the ADC lead to almost 1kW power consumption, if feasible at all [6].

While Mitola described the *ideal* SWR receiver has an ADC connected closely to antenna, he also suggested that a *practical* SWR receiver may have the ADC located at IF after frequency conversion [2]-[5].

Such a practical SWR is close to another term "software-defined radio" (SDR), which, according to Mitola [5, Section II-A], was defined by BellSouth [7] in 1995 "to describe an evolution towards greater programmability of a wireless infrastructure" [5].

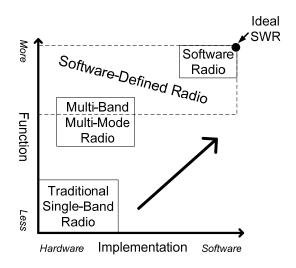

The *implementation* of a SDR (can be but) does not have to be primarily in software like a SWR, but at least the *function* of a SDR can be defined, or reconfigured, by software for different communication standards, preferably also software-upgradable to deal with future standards. Please note that there is not necessarily to be a clear boundary between SDR and non-SDR; the more programmable the better. Today's industrial multi-band multi-mode radios can be seen as an intermediate step towards SDR.

Figure 1.3 Conceived phase space of radio evolution towards greater programmability

Besides coping with multiple standards, SDR can also be an enabler for cognitive radio (CR) [8]. A CR can automatically adapt its parameters, such as carrier frequency, dynamic range, and power consumption, in response to the radio environment and user demands. The present cognitive radio application regulated by FCC [9] focuses on dynamic spectrum access in the unoccupied TV band below 1GHz, which is aimed to improve the efficiency of utilizing the scarce spectrum resources.

Till this end, we have presented the motivation of SWR and SDR as well as the actual origins of these two terms which were not always clear. However, the relationship between them can still be confusing and these two terms can be mixed up with each other. To further clarify the ambiguity between them as well as to clearly set our research scope, we summarize, in our view, their distinctions below.

Functionally, both are flexible radios but SWR also restricts the way of implementation to be primarily in software, i.e. *SWR* = *software-intensive SDR*. In our view, the scope of SDR is broader and includes SWR, while SWR represents the highest degree of flexibility in SDR. Our research targets at SDR, which is broader and more feasible for now.

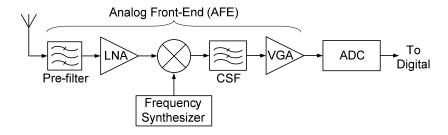

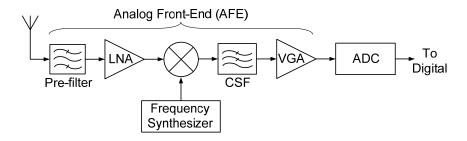

Figure 1.4 A typical block diagram of a traditional receiver

Fig. 1.3 represents, in our view, a conceived phase space of radio evolution towards greater programmability. It also indicates the scope of traditional radio, multi-band radio, SWR, and SDR, concerning the diversity of radio function and the way to implement radio function. Note that software has to run on hardware, but a SWR uses less hardware and more software, in percentage of the construction of a radio function, than traditional single-band radio and today's multi-band radio.

SDR is a wide research topic, which can range from analog to digital and from transmitter to receiver. As for SWR, the preferred technology for SDR is also CMOS, for the sake of SoC integration. For the feasibility of A/D conversion in CMOS, till this age we still need functions such as amplification, downconversion, and filtering in the analog front-end (AFE) of a radio receiver before A/D conversion.

This thesis focuses on the *analog front-end for SDR receivers* in CMOS, aiming at low power consumption to target mobile applications. There are several main challenges to realize such an AFE, which will be discussed in the next section.

#### 1.2 Challenges

Fig. 1.4 shows the typical block diagram of a traditional receiver, which is often dedicated to one band for one standard. The analog front-end (AFE) consists of an RF band-selection filter (pre-filter), low-noise amplifier (LNA), mixer, baseband channel-selection filter (CSF), and variable-gain amplifier (VGA). The challenges we talk about here will be focused on the AFE, while the synthesizer and ADC are

outside the scope of this thesis. We may also want to receive more than one standard at the same time, which can be challenging too but not in the scope of this thesis.

The key difference of a SDR receiver compared to a traditional receiver is the enhanced flexibility, i.e. it is *functionally* more flexible. To turn a traditional radio receiver into a flexible SDR receiver, considering the two main purposes of SDR, i.e. multi-standard and cognitive radio applications, we face at least the following challenges in the AFE:

- a) To deliver "good enough" NF and in-band linearity to satisfy each targeted standard in a *continuously*-covered wide frequency range;

- b) To provide "good enough" linearity or selectivity tunable over a wide frequency range, against strong out-of-band interference;

- c) To realize channel-selection filtering which can cover variable channel bandwidth, e.g. in small steps, with reconfigurable filter order;

- d) To be compatible with CMOS scaling and SoC integration.

Generally, all the above goals should better be achieved with low cost, small size, and low power consumption for large-volume (consumer) mobile applications.

To clarify their meanings, we will discuss each point of the listed challenges.

#### Points a) and b)

Points a) and b) deal with NF and linearity, which are key performance to radio receivers, and for SDR receivers, the considerations for noise and linearity are quite different from traditional radios.

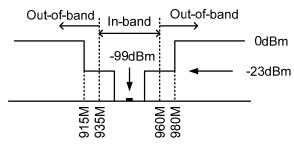

For a specific band of one standard, we may classify the received RF signal into three categories: *desired signal, in-band interference (IBI), and out-of-band interference (OBI)*. The desired signal is often a single channel in a band and IBI refers to signals in other channels than the desired in the same band while OBI refers to signals in any other bands. As an example, Fig. 1.5 shows a typical interference scenario for the GSM standard in the 900MHz band [11], indicating a

Figure 1.5 A typical blocking scenario for GSM 900MHz standard

weak desired signal at -99dBm (3dB above the sensitivity level), IBI as strong as -23dBm and OBI as strong as 0dBm.

First let's look at the *desired signal*.

For each standard, there is a sensitivity level to define the minimum available power of the desired signal received at antenna. For instance, the required sensitivity for GSM is -102dBm over a 200kHz channel while that number for DVB-H is -98dBm over a 5MHz channel. A traditional receiver should be able to provide good enough NF in a specific frequency band to satisfy the minimum signal-to-noise ratio (SNR) for successful demodulation when antenna signal is at the sensitivity level. Since a SDR receiver should cover multiple standards, it should be able to meet the required sensitivity for each *individual* standard in different bands. Furthermore, to accommodate future standards and for CR applications, it is preferred that SDR can cover a wide bandwidth *continuously*. As most mobile communication standards up to now use a band between 400MHz and 6GHz (Fig. 1.1), our focus will be on this frequency range. Typically, a *NF* < 6dB should be "good enough" for most standards in this RF range [12].

Now let's look at *interference*.

Traditional wireless standards use dedicated radio bands, so that in-band interference (IBI) can be distinguished from out-of-band interference (OBI). For a SDR aiming at covering arbitrary frequencies, the definition of IBI and OBI may become fuzzy. Still, we will use the terms IBI and OBI in this thesis as: 1) current SDR receivers often aim at covering multiple traditional radio standards which

have clear band definitions; 2) even if this is not the case, e.g. for cognitive radios, a SDR still aims at implementing selectivity, i.e. receive a signal for which the baseband bandwidth is much smaller than the RF carrier frequency. In the latter case OBI can be interpreted as "out-of-baseband interference".

For mobile communications, the IBI can be as strong as -30 to -20dBm while the OBI can be as strong as -10 to 0dBm [13]. An RF pre-filter is often employed to suppress the OBI to no larger than the IBI level. Since a desired band is often a small ratio of its carrier frequency and strong interference can be close to the desired signal frequency, the RF pre-filters often require high quality factor (Q) and sharp roll-off. Such filters are difficult to integrate on chip and are typically dedicated to one specific band, e.g. SAW band filters. As the RF pre-filters often do not suppress the IBI, the linearity of the receiver should be good enough to tolerate IBI. A receiver *in-band IIP3* > -10dBm would be "good enough" for most standards [12] [26]. As shown in Fig. 1.4, assisted by a *dedicated* RF pre-filter, a traditional receiver should be able to provide good enough linearity to counter the IBI and the suppressed OBI.

However, for SDR receivers, using a dedicated filter for each band would dramatically increase the size and cost. Therefore we prefer a *flexible* RF pre-filter, which can adjust its center frequency, bandwidth, and order for different standards. Such a filter can attenuate the OBI for each standard so that the required linearity of the SDR receiver is relaxed. However, to build such a filter at low cost is very challenging, since it usually requires multiple poles and zeros simultaneously tunable over a broadband, on top of the requirements of a traditional dedicated RF pre-filter such as high Q, sharp roll-off, and low insertion loss. Research on flexible RF pre-filters is actively ongoing, e.g. exploring the use of MEMS technology [14].

In this thesis, we look at solutions from the CMOS receiver perspective. In parallel to enhance the filter flexibility to relax the receiver linearity, we can also try to enhance the linearity of the receiver so that the requirements on the filter can be relaxed. After all, what matters is that the combined efforts from both sides, filter and receiver, meet the required system specification. Since pre-filters mainly suppress OBI, to relax those filters, the robustness of the SDR receiver to OBI is critical, while the required in-band linearity is similar to traditional receivers for each standard.

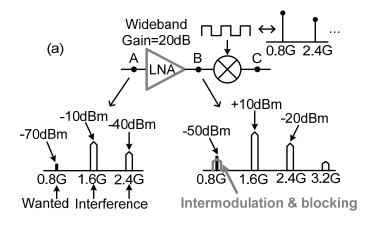

Figure 1.6 Wideband interfering mechanisms: (a) out-of-band nonlinearity; (b) harmonic mixing

At least two mechanisms generate *in-band* distortion due to OBI: 1) nonlinearity related mixing of strong out-of-band interferers via, e.g., intermodulation or cross-modulation; 2) harmonic mixing of interferers with LO harmonics due to hard-switching mixers or the use of digital LO waveforms. To clarify, we will explain these two mechanisms briefly below.

1) Out-of-band nonlinearity: Nonlinearity may generate intermodulation and harmonic distortion falling on top of the desired signal, or may desensitize a receiver due to blockers and produce cross modulation [15]. Fig. 1.6 (a)

shows an example, where a wideband LNA amplifies the desired signal at 0.8GHz and the undesired wideband interference at 1.6GHz and 2.4GHz with an equal gain of 20dB<sup>1</sup>. At the output of the LNA, the amplified interference challenges the nonlinear output impedance of the LNA and the linearity of a next-stage mixer, which can severely degrade the signal-to-noise-and-distortion ratio. Without sufficient RF pre-filtering, the out-of-band linearity can become the bottleneck since OBI is much stronger than IBI. For example, if OBI is 20dB stronger than IBI, without any attenuation of OBI, the required out-of-band IIP3 can be derived as 30dB higher than the required in-band IIP3, if aiming at that OBI generates the same distortion level as IBI

2) *Harmonic mixing*: Linear time-variant behavior in a hard-switching mixer, or equivalently multiplication with a square wave, down-converts not only the desired signal but also interference around LO harmonics. Fig. 1.6 (b) shows an example, where both the desired signal at 0.8GHz and the interference at 2.4GHz pass through the wideband LNA with equal gain. Even if the LNA is perfectly linear, the interference may directly fall on top of the desired signal after the mixer via the 3<sup>rd</sup>-order harmonic mixing. A quick calculation shows that large rejection ratio is wanted: if we want to bring harmonic responses down to the noise floor (e.g. -100dBm in 10MHz for NF=4dB), and cope with interferers between -40 and 0dBm, a harmonic rejection ratio of 60 to 100dB is needed.

Both out-of-band nonlinearity and harmonic mixing can severely degrade signal-to-distortion ratio<sup>2</sup> which directly affects the demodulation of desired signal. Therefore, in our view, a SDR receiver is not just a wideband receiver with "good enough" NF and in-band linearity, but it should also have enhanced out-of-band linearity and harmonic rejection (HR).

\_

<sup>1</sup> The gain might be lower for a clipping signal.

<sup>&</sup>lt;sup>2</sup> Signal-to-Distortion Ratio is so important to software-defined radio that it can be viewed as another interpretation of "SDR".

#### Point c)

Channel selection is used to select the desired channel and so to reduce the required dynamic range for the ADC. It is often done at baseband where high selectivity can be achieved more easily than at RF. For a traditional receiver, a fixed baseband filter to meet one dedicated standard is good enough. But for a SDR receiver, the channel-selection filter should be able to vary its characteristics, e.g. bandwidth and order, to fit the requirements of different standards. For a true SDR receiver, the filter is expected to cover a range of channel bandwidth in a certain resolution, suitable for both current and future standards. Later we will see through a couple of examples that some promising solutions have been proposed for SDR channel-selection filters.

#### Point d)

The achievable system performance can directly depend on the adopted technology platform. For example, it might be easier for technologies such as superconductor or GaAs than CMOS to achieve wider bandwidth and higher dynamic range, which are key parameters to realize the AFE of a SDR receiver. However, as described in Section 1.1, we prefer to implement SDR in CMOS as an ideal technology platform for software, and integrate analog and digital systems on one chip. Unfortunately, CMOS downscaling mainly benefits digital circuits but can put extra-ordinary challenges for analog circuits [10]. Although SoC integration may bring the opportunity of digitally-assisted calibration for analog blocks, it is challenging to integrate analog with digital on the same chip due to, e.g., simultaneous switching noise generated from millions of digital gates. Therefore, it is challenging to make SDR compatible with CMOS scaling and suitable for SoC integration.

Now we may summarize the major challenges of the analog front-end (AFE) of a SDR receiver, compared to a traditional receiver, as:

SDR Receiver AFE = Wideband Receiver AFE +

Robustness to Out-of-band Interference +

Flexible Channel-Selection Filtering +

Compatibility with CMOS Scaling and SoC Integration.

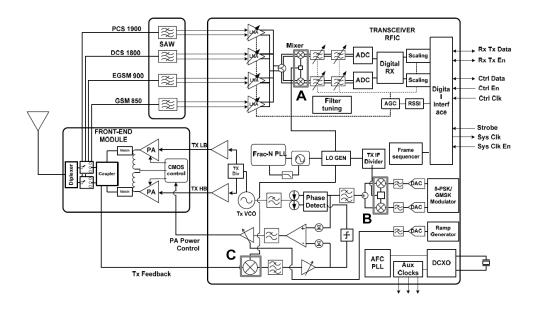

Figure 1.7 An integrated quad-band GPRS/EDGE transceiver [16]

#### 1.3 State of the Art

This section presents state-of-the-art work<sup>3</sup> related to SDR receivers, as a brief literature overview. The aims are: a) to show how the challenges pointed out in the previous section have been addressed so far by other researchers; b) to show the differences and the added values of our work (Chapter 2 to 5) compared to others'.

A traditional multi-standard receiver basically puts multiple dedicated receivers in parallel with each for one band. It is effective now for product development aiming at a quick time to market and low risk. However, this approach significantly increases system size and cost for every band that is added, for both on-chip and off-chip components. It is becoming increasingly impractical as there are already a large number of radio communication standards, while new ones are continuously being developed.

-

<sup>&</sup>lt;sup>3</sup> Please note that most work mentioned in this section is *not* "previous" work but developed in parallel to this Ph.D. project which got started in 2005. Of course, they are only valid to be "state-of-the-art" till 2009 when the thesis is written.

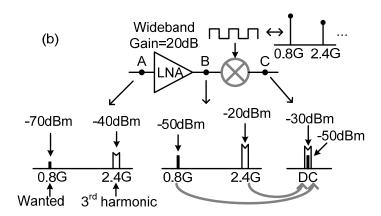

To be able to move towards SDR, it might make sense to re-think the way of designing radios. Instead of putting hardware radios in parallel for each band, we aim at sharing the same hardware for different bands. This trend of sharing hardware is evident from the multi-band multi-mode radio transceivers in today's industry, which can be considered as an intermediate step towards SDR (Fig. 1.3). A practical example is shown in Fig. 1.7 [16], which is a quad-band GSM transceiver. If we focus on the receiver side, the mixers and the baseband circuits are shared for all bands. However, in this particular example, all the targeted bands have a similar protocol (channel) bandwidth, around 200 kHz, which makes sharing the baseband hardware relatively easier. Furthermore, the LNAs and the off-chip band-filters are still dedicated for each band. The parallel LNA configuration actually can allow the freedom to select which band in use by enabling an LNA and avoid a lossy switch on the signal path. The off-chip components such as band-filters are a key bottleneck towards the SDR. Also these LNAs and band-filters cannot continuously cover a broadband.

To achieve the goal of SDR, we have recognized four major challenges in the previous section. Next we review some solutions in literature for each challenge.

#### 1.3.1 Wideband Receivers

Relevant characteristics of a wideband receiver include the input reflection coefficient ( $S_{11}$ ), gain, and NF versus frequency. A key enabling block is a wideband low-noise amplifier (LNA), which is usually the first block of a receiver chip and therefore can largely affect the  $S_{11}$ , gain, and NF of the whole receiver. For a wideband LNA, to simultaneously achieve good impedance matching, e.g.  $S_{11} < -10 dB$ , and low noise, e.g. NF < 3 dB, is challenging. Some techniques have been proposed for wideband LNAs, mainly based on noise cancelling [17] [18] or negative feedback [19] [20]. Besides, another bottleneck of wideband operation may come from the interface between LNA and mixer where the capacitive loading from mixer can limit the bandwidth of LNA.

With CMOS downscaling, the unity current-gain frequency ( $f_T$ ) of MOS transistor keeps increasing, which exceeds 100GHz for CMOS beyond the 100nm node [21]. This makes it feasible to realize receivers with a few GHz bandwidth using no or

very few inductors which cost area. In recent years, many wideband receivers have come up, partly enabled by the process advancement. They can continuously cover a wide bandwidth, say at least an octave, and therefore largely share the receiver components. These features differentiate them from the current industrial multiband multi-mode radios (Fig. 1.7).

One of the first CMOS wideband receivers was published in 2004 [22], showing a -3dB bandwidth of 200MHz to 2.2GHz and implemented in 0.18 $\mu$ m technology. It is a zero-IF receiver employing noise-cancelling LNA and passive mixer. By an extensive use of high effective gate-source voltages ( $V_{GS}$ - $V_{TH}$ ) and resistive degeneration, it achieves +1dBm IIP3 at a conversion gain of around 25dB. However, this comes at the cost of a relatively high NF of 7dB and a power consumption of 200mW.

The UCLA SDR receiver [23] published in 2006 is a zero-IF receiver aming at the 800MHz to 5GHz range in 90nm CMOS, including baseband filters and an LO generator. The noise-cancelling LNA exploits inductive peaking to extend the bandwidth at the input and the interface with mixer and a passive mixer is adopted for low 1/f noise and high IIP2. The LNA and the mixer operate at a 2.5V supply for high dynamic range, consuming 45mW. At a full-gain setting, the LNA and mixer achieves 30dB gain, 5dB NF, and -15dBm IIP3 up to 2.4GHz, while at a medium-gain setting, it achieves 21dB gain, 9dB NF, and -3.5dBm IIP3. However, the performance of the whole receiver is only presented for two frequencies: 900MHz and 2.4GHz. No measurement data are shown beyond 2.4GHz.

The IMEC SDR transceiver [24] [25] published in 2007 consists of a zero-IF wideband receiver in 0.13µm CMOS. The publications stress on extensive programmability aiming at an adaptive power/performance trade-off. To resolve the conflict of low 1/f noise required below 500MHz RF and fast transistors required for 5GHz, two separate LNAs are used: a noise-cancelling LNA for 100MHz to 2.5GHz and an inductive-degeneration LNA for 2.5GHz to 6GHz. Its second generation [26] published in 2009 is a 0.1-to-5GHz zero-IF receiver implemented in 45nm CMOS, including baseband filter and frequency synthesizer. A passive mixer follows two LNAs, an active-feedback LNA for 0.1GHz to 1.5GHz and a resistive-feedback LNA for 1.5GHz to 5GHz. The dual-band LNAs use switchable low-Q inductive peaking to cover the whole wide band in four sub-

bands. The receiver sensitivity is verified for 6 different standards, from DVB-H at 600MHz to 802.11n at 5GHz, achieving an NF from 2.3dB to 6.5dB.

In parallel to [24-26], a similar approach of realizing a SDR transceiver aiming at a power/performance trade-off has also been developed in industry. As an example, the Bitwave "Softransceiver" [27] is configurable from 700MHz to 3.8GHz and is compliant with cellular, WLAN, and broadcast standards. Each element of the transceiver's single-component transmit and receive chain can be software-optimized for a given standard. The receiver integrates an analog front-end, ADCs and frequency synthesizers, in 0.13µm CMOS. However, detailed performance data such as NF and linearity are not available.

Besides, many wideband receivers have been developed for ultra-wideband (UWB) applications [28] [29]. Some of their techniques can also be useful to SDR. The "Blixer" [30] published in 2008 is a wideband zero-IF receiver using a combined balun-LNA-I/Q-mixer topology. It stacks an I/Q current-commutating mixer on top of a noise-canceling balun-LNA, thus reusing the bias current. The real part of the impedance of all RF nodes is kept low, and the voltage gain is not created at RF but at baseband where capacitive loading is no problem. Thus the bandwidth limitation is relaxed at the interface between the LNA and the mixer in a conventional receiver employing a voltage-gain LNA. A large RF bandwidth is thereby achieved without using inductors for bandwidth extension. This feature will also be exploited in one of our designs (Chapter 5). Implemented in 65nm CMOS, it achieves an 18dB gain, a flat NF of 5.5dB from 500MHz to 7GHz, and a -3dBm IIP3 while consuming only 16mW from a 1.2V supply. However, 1/f noise from the mixer which conducts DC current is a challenge for SDR applications.

*In summary*, most published wideband receivers use a zero-IF architecture for high-level integration and adopt a passive mixer for low 1/f noise. Both noise-cancelling [22] [23] [25] [30] and negative-feedback [26] [28] [29] LNAs have found applications. As demonstrated [23] [26] [30], using CMOS technology beyond 100nm node, a receiver RF bandwidth from a few hundred MHz to more than 5 GHz can be achieved with an NF < 6dB at a low power consumption, say a few tens of mW, suitable for mobile applications. Besides, some of the presented receivers can satisfy the in-band IIP3 > -10dBm [22] [28-30], simultaneously with NF < 6dB.

However, these wideband receivers mainly focus on realizing a wideband operation with good enough NF and in-band linearity for each band, more or less assuming an RF pre-filter will take care of strong out-of-band interference. Therefore, although these receivers can share the on-chip components for multiple bands, a dedicated narrowband RF pre-filter is still needed for each band thus adding size and cost. There is clearly room for improvement to make wideband receivers robust to out-of-band interference.

#### 1.3.2 Robustness to Out-of-Band Interference

CMOS scaling is beneficial for wide bandwidth, but not for linearity because: a) more short-channel effects, e.g. channel-length modulation and mobility reduction, bring larger distortion related to transistor output impedance [31]; b) lowered supply voltage sets tighter constraints for handling large interference.

The linearity challenge in scaling CMOS is especially problematic for OBI, which can be much stronger than IBI. In a wideband receiver, out-of-band interference can generates in-band distortion via nonlinearity or harmonic mixing, as described in Section 1.2. Some wideband receivers, e.g. [23], claim to be able to completely get rid of the RF pre-filter however the achieved performance is not convincing. For example, the reported IIP3 of -3.5dBm is for a medium-gain setting, which cannot simultaneously guarantee the required sensitivity level while the derived IIP3 for the full-gain setting is around -15dBm. On the other hand, without any RF pre-filtering, the required IIP3 can be as high as, e.g., +30dBm for a Bluetooth radio [32].

To counter the extra-ordinary challenge due to OBI, there are a few measures reported in literature to relax the pre-filtering requirements, as discussed below one by one.

#### a) Out-of-Band Nonlinearity

One potential solution is to integrate some band-selectivity on chip. However, high-performance LC filtering is still difficult to realize in digital CMOS due to, for instance, large size and low *Q* of monolithic inductors. *Q*-enhanced band-pass

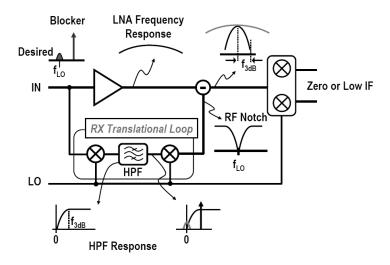

Figure 1.8 Feedforward blocker filtering concept [41]

filters [33] [34] have been proposed to improve the inductor Q using active components as negative resistance. However, this often comes at the cost of noise and linearity degradation. Also, the frequency tuning range is still limited by the LC tank, typically tuned via controlled capacitors. As shown by the benchmark in [33], the achieved tuning range so far is less than 25%, which means that more than a few filters are needed to cover a broad band for SDR applications. On the other hand, smaller filter size and larger tuning range (e.g. 100%) can be achieved using pure active band-pass filters without passive inductors [35] but at the cost of degraded dynamic range. Notch filters with a band-stop characteristic using a Q-enhanced LC-tank have been applied in some wideband receivers to suppress specific interference, e.g. for UWB applications [36] [37]. However, the limitation is that the interference should be predictable and concentrated in a small frequency range.

LNA linearization techniques have been proposed to achieve an IIP3 in excess of +15dBm via, for instance, derivative superposition methods [38] [39]. Some drawbacks of these techniques are [40]: 1) they often rely on two nonlinearity mechanisms that compensate each other but don't automatically match, so that some kind of fine tuning is needed, compromising the robustness to process spread; 2) they mostly rely on modeling of the weakly nonlinear region so that high IIP3 is

only achieved for low input interference power while there is only limited or even no benefit for strong interference.

Recently, a flexible blocker filtering technique has been presented to cancel blockers at the output of the LNA [41], as shown in Fig. 1.8. Blocker reduction is achieved by means of an auxiliary feedforward path, using two mixers with a high-pass filter (HPF) in between. This auxiliary path conducts the undesired interferers and suppresses them by subtracting them from the main signal path at the output of the LNA. However, it comes at significant cost in terms of noise and power consumption due to the additional feedforward signal path and its performance relies on the matching between the main path and the auxiliary path. We will see later in Chapter 5 that an equivalent functionality can be achieved with much simpler hardware.

#### b) Harmonic Mixing

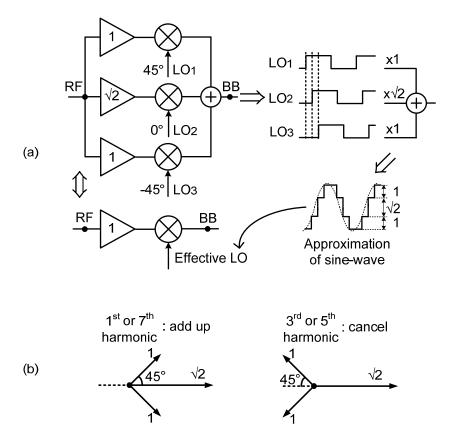

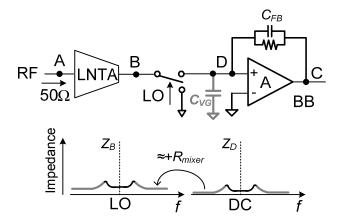

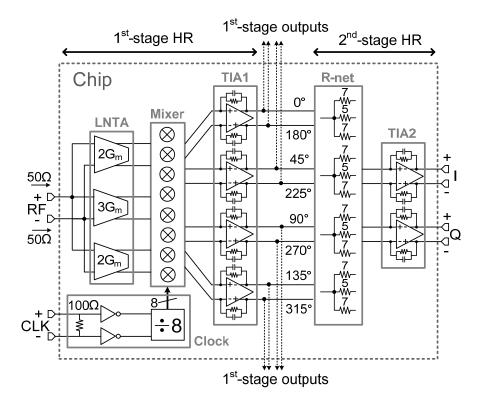

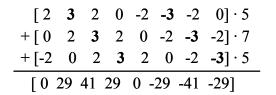

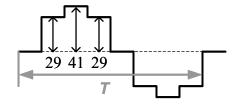

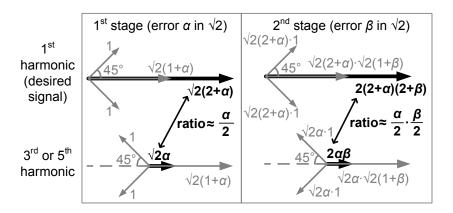

Harmonic-rejection (HR) mixers using multi-phase square-wave LOs driving parallel operating mixers have been proposed [42]. Fig. 1.9 (a) shows an example, where the weighted current outputs add up to approximate mixing with a sine-wave LO. All even-order harmonics can be suppressed by a balanced LO. The combination of an amplitude ratio of  $1:\sqrt{2}:1$  and an 8-phase LO (equidistant 45°) can reject the  $3^{rd}$  and  $5^{th}$  harmonics, as shown in the vector diagram of Fig. 1.9 (b). The  $7^{th}$  harmonic is not rejected and still needs to be removed by filtering, but the filter requirement is strongly relaxed compared to the case of a normal double-balanced I/Q mixer whose first un-rejected harmonic is the  $3^{rd}$  order. However, the achievable HR ratio is typically limited to 30-to-40dB [23] [43] [44] by the accuracy of the LO phases and the amplitude ratios, e.g. the irrational amplitude ratio of  $1:\sqrt{2}:1$ .

To improve the limited HR ratio in a mixer, the state-of-the-art wideband TV tuners rely on RF-tracking filters together with HR mixers [43] [44] to guarantee more than 65dB HR ratio. However, these tracking filters cost power, take area, and introduce extra noise and distortion. For example, the 4<sup>th</sup>-order band-pass Gm-C tracking filter in [43] achieves a 7dB gain, a 17dB NF, and a +7dBm IIP3 while consuming 72mW power.

Figure 1.9 (a) Block diagram of a traditional HR mixer; (b) its vector diagram

As a summary, we see some measures have been taken in both areas, i.e. out-of-band nonlinearity and harmonic mixing. However, either they are not yet suitable for SDR applications due to insufficient flexibility, e.g. integrated LC filters, or they may significantly compromise other performance such as power and noise, e.g. tracking filters for TV tuners and blocker filtering via an auxiliary path. Some other techniques can be flexible and do not degrade other performance much, but are sensitive to mismatch and process spread, e.g. LNA linearization and HR mixers. Besides, of all the aforementioned techniques, their selectivity cannot yet match off-chip RF pre-filters such as SAW filters. To this end, we may conclude that there is a lot of room for improvement with respect to SDR receiver's robustness to out-of-band interference.

#### 1.3.3 Flexible Baseband Channel Selection

Generally for the baseband-filter design, there exists a trade-off between bandwidth, noise, and filter order versus power consumption. Two classes of filters have been proposed for flexible SDR receivers: continuous-time (CT) and discrete-time (DT) filters. Both have shown promising results.

The IMEC SDR transceiver [24] applies CT baseband filters constructed via a cascade of two active- $G_m$ -RC biquads and a Rauch biquad. It may continuously cover a bandwidth of 0.35MHz to 23.5MHz with a programmable  $2^{nd}$ ,  $4^{th}$  or  $6^{th}$  order. It can achieve a 12-bit frequency-tuning resolution via a combination of a 5-bit coarse tuning using a resistor array and a 7-bit fine tuning using a capacitor array [45]. Their second-generation SDR receiver also employs CT baseband filtering [26].

Flexible baseband DT filters have also been developed. The UCLA SDR receiver [23] uses a passive switched–capacitor filter demonstrated for the GSM and the 802.11g standards, tunable via changing sampling rate and decimation ratios. However, continuous frequency tunability was not shown. The active- $G_m$  switched-capacitor filter from NEC [46] can cover 0.4MHz to 30MHz continuously tunable via a DT transconductor controlled by clock duty cycle, with a  $2^{nd}$  or  $4^{th}$  order characteristic. The frequency-tuning resolution was not mentioned but depends on the resolution of the clock duty cycle.

The baseband filter in the Bitwave "Softransceiver" [27] can continuously cover the bandwidth of 25kHz to 20MHz in more than 1000 steps and can support all major cellular, WLAN, and broadcast standards. It is unclear whether the filter is in CT or DT implementation.

From the above examples, we can see that many promising solutions have been demonstrated for the flexible baseband filtering and basically can satisfy the SDR applications. Especially, some have been built into products such as [27].

#### 1.3.4 Compatibility with CMOS Scaling and SoC Integration

As shown in Section 1.3.1, using new design techniques, many wideband radio receivers have been demonstrated in advanced CMOS technology, e.g. 90nm [23], 65nm [30], and 45nm [26]. However, it is another degree of challenge to integrate radio transceivers and digital (de)modulators on the same chip, due to, e.g. digital switching noise.

Direct RF-sampling receivers seem to be a good candidate, both for better compatibility with CMOS scaling [47]-[49] and SoC integration [50] [51]. They sample the signal early in the receiver chain *before or simultaneously with* downconversion, instead of *after* downconversion which is done in RF-mixing receivers. A few RF-sampling receivers for commercial products have been presented [48]-[51], including what is claimed to be the first published [51] commercial SoC for quad-band GSM in 90nm baseline digital CMOS with no analog extension.

However, all of these RF-sampling receivers are dedicated to one narrowband standard and all the aforementioned wideband receivers in Section 1.3.1 are based on RF mixing. Further research is needed to evaluate the suitability of RF sampling for SDR applications, and we will address this subject in Chapter 2.

Till this point, we have discussed the challenges of realizing a SDR receiver and some state-of-the-art solutions in literature. The next section will discuss our research objectives and the challenges we are going to address, while also clarifying the added value to other work.

#### 1.4 Research Objectives

After summarizing the previous section, we may conclude that lots of solutions have been proposed for wideband receivers and flexible baseband filtering, showing promising results. However, the other two challenges, of handling OBI in a wideband receiver and of realizing a SDR in a downscaled CMOS with SoC integration, still have a long way to go.

This thesis aims at finding: 1) techniques to improve the robustness of wideband receivers to OBI; 2) techniques for wideband receivers compatible with CMOS scaling and SoC integration.

To address the challenge due to OBI, we should look at both mechanisms: out-of-band nonlinearity and harmonic mixing. After amplification by an LNA, the burden of the nonlinearity is mainly on the mixer while harmonic mixing also happens in the mixer. Therefore, this thesis will focus on *frequency translation* related innovations to improve the receivers' robustness to OBI. The work aims at removing RF pre-filters or at least drastically relaxing their requirements.

As described in the previous section, RF-sampling receivers can bring two advantages: compatibility with CMOS scaling and SoC integration. However, as will be discussed in Chapter 2, current RF-sampling techniques do not directly fit wideband SDR applications. To our knowledge, all the wideband receivers shown by other researchers so far are based on RF mixing but not RF sampling. We will explore new RF-sampling techniques more suitable for wideband SDR receivers, which also involve new *frequency translation* techniques.

The title of the thesis refers to the above mentioned goals. This thesis mainly explores "frequency translation techniques" to improve the "interference-robust" characteristic of "software-defined radio receivers" and to make them compatible with CMOS scaling and SoC integration. Moreover, the thesis also describes some filter and amplifier techniques which support interference-robustness.

Based on the foregoing discussions, now we set our concrete research objectives:

- Develop new RF-sampling receivers for wideband applications

- Enhance the out-of-band linearity of wideband receivers

- Improve the robustness of harmonic rejection to mismatch

#### 1.5 Thesis Organization

The rest of the thesis is organized as follows:

Chapter 2 discusses fundamental differences of frequency translation (FT) techniques for radio receivers, via a classification and comparison for FT techniques based on mixing and sampling principles [52]. This also leads to the definition of a discrete-time (DT) mixing technique. Moreover, we will evaluate the suitability of RF-mixing and RF-sampling receivers to SDR and analyze the challenges of applying RF sampling to wideband receivers [53].

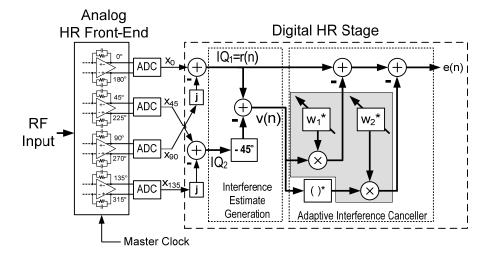

Chapter 3 elaborates the DT mixing technique [52] [54], which can make RF sampling more suitable to SDR receivers by achieving two wideband features: wideband quadrature demodulation and wideband harmonic rejection. To verify the concept, a 200-to-900MHz DT-mixing downconverter with 8-times oversampling and 2<sup>nd</sup>-to-6<sup>th</sup> HR is implemented in 65nm CMOS. Chapter 4 describes a tunable LC filter and a linearized LNA [55] [56], applied as pre-stages of the DT-mixing downconverter to construct a complete RF-sampling receiver achieving a minimum NF as low as 0.8dB. To make the receiver more robust to interference, the tunable LC filter improves the HR ratio flexibly and the LNA exploits a new linearity enhancement technique.

Furthermore, Chapter 5 proposes two frequency translation techniques for an interference-robust SDR receiver [57] [58], one to improve the out-of-band linearity and the other to make the HR robust to mismatch. To demonstrate these two concepts, a 65nm CMOS receiver based on RF mixing shows that +3.5dBm in-band IIP3 and +16dBm out-of-band IIP3 can be achieved. More than 60dB HR ratio is measured over 40 randomly-selected chips while more than 80dB becomes possible with digitally-enhanced HR. The proposed accurate multi-phase LO generator works up to 0.9GHz while the RF bandwidth is measured up to 6GHz.

Chapter 6 draws conclusions, summarizes the main contributions of this work, and suggests some future research directions.

The appendix contains two important analyses. Appendix *A* derives the wideband transfer function of baseband impedance to RF through mixer switches (Chapter 5), namely "mix-impedance". Appendix *B* performs a statistical analysis for HR considering random amplitude and phase errors, to quantify the required accuracy to achieve a certain HR ratio (Chapter 5).

#### 1.6 References

- [1] C. Taylor, "Global mobile penetration to reach 75% by 2011", [Online], Available:

- http://www.theregister.co.uk/2007/10/26/mobile pentration research/

- [2] J. Mitola, "Software radios-survey, critical evaluation and future directions," *National Telesystems Conference, (NTC)*, pp.13/15-13/23, May 1992

- [3] J. Mitola, "Software radios: Survey, critical evaluation and future directions," *IEEE Aerospace and Electronic Systems Magazine*, vol.8, no.4, pp.25-36, Apr. 1993

- [4] J. Mitola, "The software radio architecture," *IEEE Communications Magazine*, vol.33, no.5, pp.26-38, May 1995

- [5] J. Mitola, "Software radio architecture: a mathematical perspective," *IEEE J. Selected Areas in Communications*, vol.17, no.4, pp.514-538, Apr. 1999

- [6] E.A.M. Klumperink, R. Shrestha, E. Mensink, V.J. Arkesteijn, B. Nauta, "Cognitive radios for dynamic spectrum access polyphase multipath radio circuits for dynamic spectrum access," *IEEE Communications Magazine*, vol.45, no.5, pp.104-112, May 2007

- [7] The Software Defined Radio Request for Information. Atlanta, GA: BellSouth, Dec. 1995

- [8] J. Mitola, G.Q. Maguire, "Cognitive radio: making software radios more personal," *IEEE Personal Communications*, vol.6, no.4, pp.13-18, Aug. 1999

- [9] The Federal Communications Commission (FCC), "Notice for Proposed Rulemaking (NPRM 03 322): Facilitating Opportunities for Flexible, efficient, and Reliable Spectrum Use Employing Spectrum agile Radio Technologies", *ET Docket No. 03 108*, Dec. 2003

- [10] A.-J. Annema, B. Nauta, R. van Langevelde, H. Tuinhout, "Analog circuits in ultra-deep-submicron CMOS," *IEEE J. Solid-State Circuits*, vol.40, no.1, pp. 132-143, Jan. 2005

- [11] GSM Technical Specification 05.05, European Telecommunications Standards Institute, Sophia Antipolis, France, 1992

- [12] M. Brandolini, P. Rossi, D. Manstretta, F. Svelto, "Toward multistandard mobile terminals - fully integrated receivers requirements and architectures," *IEEE Trans. Microwave Theory and Techniques*, vol.53, no.3, pp. 1026-1038, Mar. 2005

- [13] D. Manstretta, N. Laurenti and R. Castello, "A Reconfigurable Narrow-Band MB-OFDM UWB Receiver Architecture," *IEEE Trans. Circuits and Systems II: Express Briefs*, vol.55, no.4, pp.324-328, Apr. 2008

- [14] C.T.-C. Nguyen, "Vibrating RF MEMS for next generation wireless applications," *IEEE CICC*, *Proc.*, pp. 257-264, Oct. 2004

- [15] B. Razavi, "RF Microelectronics", Prentice Hall, Upper Saddle River, NJ, 1998

- [16] R. Pullela, S. Tadjpour, D. Rozenblit, et. al. "An integrated closed-loop polar transmitter with saturation prevention and low-IF receiver for quad-band GPRS/EDGE," *IEEE ISSCC*, *Dig. Tech. Papers*, pp.112-113,113a, Feb. 2009

- [17] F. Bruccoleri, E.A.M. Klumperink, B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling," *IEEE J. Solid-State Circuits*, vol.39, no.2, pp. 275-282, Feb. 2004

- [18] C.-F. Liao, S.-I. Liu, "A Broadband Noise-Canceling CMOS LNA for 3.1–10.6-GHz UWB Receivers," *IEEE J. Solid-State Circuits*, vol.42, no.2, pp.329-339, Feb. 2007

- [19] J.-H.C. Zhan, S.S. Taylor, "A 5GHz resistive-feedback CMOS LNA for low-cost multi-standard applications," *IEEE ISSCC, Dig. Tech. Papers*, pp.721-730, Feb. 2006

- [20] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, M. Kuijk, "Low-Area Active-Feedback Low-Noise Amplifier Design in Scaled Digital CMOS," *IEEE J. Solid-State Circuits*, vol.43, no.11, pp.2422-2433, Nov. 2008

- [21] H.S. Bennett, R. Brederlow, J.C. Costa, P.E. Cottrell, W.M. Huang, A.A. Immorlica, et. al., "Device and technology evolution for Si-based RF integrated circuits," *IEEE Trans. Electron Devices*, vol.52, no.7, pp. 1235-1258, July 2005

- [22] V.J. Arkesteijn, E.A.M. Klumperink, B. Nauta, "A wideband high-linearity RF receiver front-end in CMOS," ESSCIRC, Proc., pp. 71-74, Sept. 2004

- [23] R. Bagheri, A. Mirzaei, S. Chehrazi, et. al. "An 800MHz to 5GHz Software-Defined Radio Receiver in 90nm CMOS," *IEEE ISSCC*, *Dig. Tech. Papers*, pp.1932-1941, Feb. 2006

- [24] J. Craninckx, M. Liu, D. Hauspie, et. al., "A Fully Reconfigurable Software-Defined Radio Transceiver in 0.13μm CMOS," *IEEE ISSCC*, *Dig. Tech. Papers*, pp.346-607, Feb. 2007

- [25] M. Ingels, C. Soens, J. Craninckx, et. al., "A CMOS 100MHz to 6GHz software defined radio analog front-end with integrated pre-power amplifier," *ESSCIRC, Proc.*, pp.436-439, Sept. 2007

- [26] V. Giannini, P. Nuzzo, C. Soens, et. al., "A 2mm<sup>2</sup> 0.1-to-5GHz SDR receiver in 45nm digital CMOS," *IEEE ISSCC, Dig. Tech. Papers*, pp.408-409, Feb. 2009

- [27] BitWave Semiconductor, The BW1102 Softransceiver Product Brief, [Online], Available: http://www.bitwavesemiconductor.com/pdf/1014BWS06SLS-G-SoftransceiverProductBrief.pdf

- [28] R. van de Beek, J. Bergervoet, H. Kundur, et. al., "A 0.6-to-10GHz Receiver Front-End in 45nm CMOS," *IEEE ISSCC, Dig. Tech. Papers*, pp.128-601, Feb. 2008

- [29] D. Leenaerts, R. van de Beek, J. Bergervoet, et. al., "A 65nm CMOS inductorless triple-band-group WiMedia UWB PHY," *IEEE ISSCC*, *Dig. Tech. Papers*, pp.410-411,411a, Feb. 2009

- [30] S. Blaakmeer, E.A.M. Klumperink, D, Leenaerts, B. Nauta, "A Wideband Balun LNA I/Q-Mixer combination in 65nm CMOS," *IEEE ISSCC, Dig. Tech. Papers*, pp.326-617, Feb. 2008

- [31] B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2000

- [32] V. Arkesteijn, "Analog front-ends for software-defined radio receivers", *Ph.D. Dissertation*, University of Twente, Netherlands, 2007

- [33] B. Georgescu, I.G. Finvers, F. Ghannouchi, "2GHz Q-Enhanced Active Filter With Low Passband Distortion and High Dynamic Range," *IEEE J. Solid-State Circuits*, vol.41, no.9, pp.2029-2039, Sept. 2006

- [34] X. He, W.B. Kuhn, "A 2.5-GHz low-power, high dynamic range, self-tuned Q-enhanced LC filter in SOI," *IEEE J. Solid-State Circuits*, vol.40, no.8, pp. 1618-1628, Aug. 2005

- [35] Y. Wu, X. Ding, M. Ismail, H. Olsson, "RF bandpass filter design based on CMOS active inductors," *IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing*, vol.50, no.12, pp. 942-949, Dec. 2003

- [36] A. Valdes-Garcia, C. Mishra, F. Bahmani, J. Silva-Martinez, E. Sanchez-Sinencio, "An 11-Band 3–10 GHz Receiver in SiGe BiCMOS for Multiband OFDM UWB Communication," *IEEE J. Solid-State Circuits*, vol.42, no.4, pp.935-948, Apr. 2007

- [37] A. Vallese, A. Bevilacqua, C. Sandner, M. Tiebout, A. Gerosa, A. Neviani, "Analysis and Design of an Integrated Notch Filter for the Rejection of Interference in UWB Systems," *IEEE J. Solid-State Circuits*, vol.44, no.2, pp.331-343, Feb. 2009

- [38] V. Aparin, L.E. Larson, "Modified derivative superposition method for linearizing FET low-noise amplifiers," *IEEE Trans. Microwave Theory and Techniques*, vol.53, no.2, pp.571-581, Feb. 2005

- [39] W.-H. Chen, G. Liu, B. Zdravko, A.M. Niknejad, "A Highly Linear Broadband CMOS LNA Employing Noise and Distortion Cancellation," *IEEE J. Solid-State Circuits*, vol.43, no.5, pp.1164-1176, May 2008

- [40] E.A.M. Klumperink, B. Nauta, "Systematic comparison of HF CMOS transconductors," *IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing*, vol.50, no.10, pp. 728-741, Oct. 2003

- [41] H. Darabi, "A Blocker Filtering Technique for SAW-less Wireless Receivers," *IEEE J. Solid-State Circuits*, vol.42, no.12, pp.2766-2773, Dec. 2007

- [42] J.A. Weldon, R.S. Narayanaswami, J.C. Rudell, *et. al.*, "A 1.75-GHz highly integrated narrow-band CMOS transmitter with harmonic-rejection mixers," *IEEE J. Solid-State Circuits*, vol.36, no.12, pp.2003-2015, Dec. 2001

- [43] S. Lerstaveesin, M. Gupta, D. Kang, B.-S. Song, "A 48–860 MHz CMOS Low-IF Direct-Conversion DTV Tuner," *IEEE J. Solid-State Circuits*, vol.43, no.9, pp.2013-2024, Sept. 2008

- [44] F. Gatta, R. Gomez, Y. Shin, *et al.*, "An Embedded 65nm CMOS Low-IF 48MHz-to-1GHz Dual Tuner for DOCSIS 3.0", *IEEE ISSCC, Dig. Tech. Papers*, pp.122-123, Feb. 2009

- [45] V. Giannini, J. Craninckx, S. D'Amico, A. Baschirotto, "Flexible Baseband Analog Circuits for Software-Defined Radio Front-Ends," *IEEE J. Solid-State Circuits*, vol.42, no.7, pp.1501-1512, July 2007

- [46] M. Kitsunezuka, S. Hori, T. Maeda, "A Widely-Tunable Reconfigurable CMOS Analog Baseband IC for Software-Defined Radio," *IEEE ISSCC*, *Dig. Tech. Papers*, pp.66-595, Feb. 2008

- [47] K. Muhammad, R.B. Staszewski, "Direct RF sampling mixer with recursive filtering in charge domain," *IEEE ISCAS, Proc*, pp. I-577-80 Vol.1, May 2004

- [48] R.B. Staszewski, K. Muhammad, D. Leipold, et. al., "All-digital TX frequency synthesizer and discrete-time receiver for Bluetooth radio in 130-nm CMOS," *IEEE J. Solid-State Circuits*, vol.39, no.12, pp. 2278-2291, Dec. 2004

- [49] F. Montaudon, R. Mina, S. Le Tual, et. al., "A Scalable 2.4-to-2.7GHz Wi-Fi/WiMAX Discrete-Time Receiver in 65nm CMOS," *IEEE ISSCC, Dig. Tech. Papers*, pp.362-619, 3-7 Feb. 2008

- [50] K. Muhammad, H. Yo-Chuol, T.L. Mayhugh, et. al., "The First Fully Integrated Quad-Band GSM/GPRS Receiver in a 90-nm Digital CMOS Process," *IEEE J. Solid-State Circuits*, vol.41, no.8, pp.1772-1783, Aug. 2006

- [51] R.B. Staszewski, D. Leipold, O. Eliezer, et. al., "A 24mm<sup>2</sup> Quad-Band Single-Chip GSM Radio with Transmitter Calibration in 90nm Digital CMOS," *IEEE ISSCC, Dig. Tech. Papers*, pp.208-607, Feb. 2008

- [52] Z. Ru, E.A.M. Klumperink, B. Nauta, "Discrete-Time Mixing Receiver Architecture for RF-Sampling Software-Defined Radio", submitted to *IEEE J. Solid-State Circuits*

- [53] Z. Ru, E.A.M. Klumperink, B. Nauta, "On the Suitability of Discrete-Time Receivers for Software-Defined Radio," *IEEE ISCAS*, pp.2522-2525, May 2007

- [54] Z. Ru, E.A.M. Klumperink, B. Nauta, "A Discrete-Time Mixing Receiver Architecture with Wideband Harmonic Rejection", *IEEE ISSCC, Dig. Tech. Papers*, pp.322-323., Feb. 2008

- [55] Z. Ru, E.A.M. Klumperink, C.E. Saavedra, B. Nauta, "A tunable 300–800MHz RF-sampling receiver achieving 60dB harmonic rejection and 0.8dB minimum NF in 65nm CMOS," *IEEE RFIC Symposium*, pp.21-24, June 2009

- [56] Z. Ru, E.A.M. Klumperink, C.E. Saavedra, B. Nauta, "A 300-800MHz Tunable Filter and Linearized LNA applied in a Low-Noise Harmonic-Rejection RF-Sampling Receiver", submitted to *IEEE J. Solid-State Circuits*, *Special Issue on RFIC Symposium* 2009

- [57] Z. Ru, E.A.M. Klumperink, G.J.M. Wienk, B. Nauta, "A software-defined radio receiver architecture robust to out-of-band interference," *IEEE ISSCC, Dig. Tech. Papers*, pp.230-231, Feb. 2009

- [58] Z. Ru, N.A. Moseley, E.A.M. Klumperink, B. Nauta, "Digitally-Enhanced Software-Defined Radio Receiver Robust to Out-of-Band Interference", accepted by *IEEE J. Solid-State Circuits*, Dec. 2009

## Chapter 2

# Frequency Translation Fundamentals

From Section 1.4, we know that frequency translation (FT) techniques will be a focus of this thesis. This chapter discusses fundamental differences among various FT techniques for radio receivers, with an emphasis on downconversion. It serves as a theoretical base for the follow-up chapters (Chapter 3 to 5) which will present circuits and systems around various types of FT techniques.

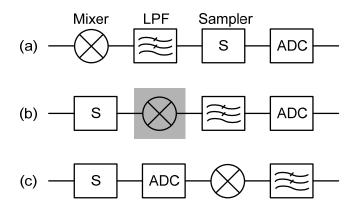

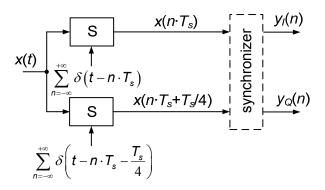

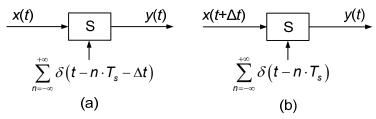

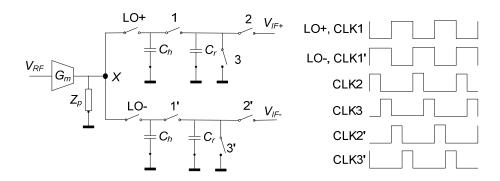

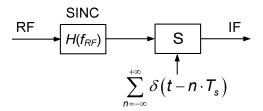

Chapter 2 starts with a brief introduction on the main reasons for applying FT in radios in Section 2.1. To clarify different downconversion techniques, in Section 2.2 we present a classification of them [1]. This also leads to the definition of a discrete-time (DT) mixing technique which is the subject of the next two chapters. To further clarify the classification criteria, Section 2.3 compares mixing and sampling principles, stressing on their fundamental distinctions. Based on the classification, Section 2.4 comes up with three receiver architectures and discusses their suitability to SDR applications. Among these architectures, RF-sampling receivers show some advantages on the compatibility with CMOS scaling and SoC integration. However, traditional RF-sampling techniques also present some drawbacks for wideband SDR applications. Therefore, in Section 2.5, we analyze the challenges of applying RF sampling to wideband receivers [2]. These challenges can be solved via techniques presented in the next chapter. Chapter 2 ends with conclusions (Section 2.6) and references (Section 2.7).

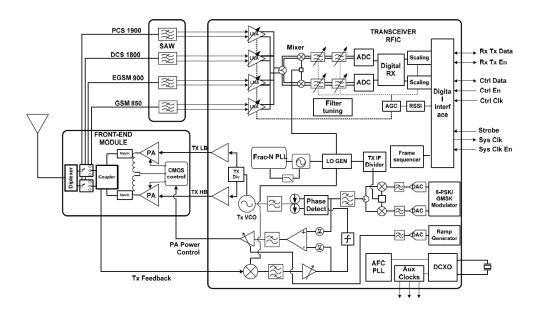

Figure 2.1 An integrated quad-band GPRS/EDGE transceiver [3]

## 2.1 Why Frequency Translation

Frequency translation (FT) includes frequency upconversion and downconversion. It can be found in many radios, e.g. as a *bridge* between baseband and RF parts, to process data at baseband while transmitting and receiving antenna signals at radio frequency, typically in the range of hundreds of MHz to a few GHz.

Fig. 2.1 shows an example of a quad-band GSM radio transceiver [3], indicating the blocks with FT functions in both receivers and transmitters. In the receiver, an RF quadrature mixer A is used between the LNA and the baseband filter, to down-convert the RF signal received at the antenna to baseband for the analog-to-digital converter (ADC). In the transmitter, an IF quadrature mixer B is used between baseband filter and IF filter, to up-convert the baseband signal from digital-to-analog converter (DAC) to be an input of the phase detector in the transmitter translational loop. Another mixer C is applied as a part of the translational loop to down-convert the transmitter feedback signal to be the other input of the phase detector.

Figure 2.2 Block diagram of a typical radio receiver indicating AFE

There are two main reasons why we want FT in a radio: *feasibility and power consumption*. To explain this further, we first look at the receiver side.

In fact, a major function of an analog front-end (Fig. 2.2) is to assist in the conversion of an antenna signal into the digital domain<sup>1</sup>, for advanced signal processing. Simply put, the analog front-end makes the job of the ADC easier with respect to the required speed and dynamic range (DR). The down-mixer is responsible for reducing the speed, from RF to baseband. Two other important blocks are the channel-selection filter (CSF), which suppresses interferers to reduce the required DR of an ADC, and the variable-gain amplifier (VGA), which controls the gain to reduce the DR of the desired signal and the unsuppressed interferers.

Without downconversion, the ADC in a radio receiver is often *unfeasible*, due to a higher speed required at a high DR. For instance, a GSM receiver can require an ADC resolution as high as 14 bits [4], even with the assistance of a VGA and a channel filter. Without downconversion, reception of a GSM signal at 1.9GHz asks for a 14-bit ADC running at a speed of at least 3.8GS/s (Nyquist rate). However, the reported state-of-the-art CMOS ADCs can only achieve 34dB (5.5-bit) signal-to-noise-and-distortion ratio (SNDR) at 2.5GS/s with 1.1GHz bandwidth [5] or 56dB (9-bit) SNDR at 1GS/s with 500MHz bandwidth [6]. An overview of the top ADCs published in recent years can be found in [7] but none is even close to the desired performance of about 4GS/s and 14 bits.

\_

<sup>&</sup>lt;sup>1</sup> Otherwise pure analog demodulation is also possible.

Please note that the actual required ADC resolution, without downconversoin ahead, is likely to be higher than what is typically required today for an ADC after downconversion. A key reason is that a band-pass (BP) channel-selection filter used in case of no downconversion is more challenging to make than a low-pass (LP) one. In the end, such a BP channel filter may be even not feasible or achieved with lower order and Q-factor. This can require a higher-resolution ADC due to a higher DR caused by stronger in-band interference since the BP channel selection is less effective. Moreover, if including out-of-band interference into consideration, e.g. for SDR applications, the requirement on the ADC will be even more stringent.

One step back. Even if such an ADC (and BP channel filter) can be feasible in the future, the *power consumption* of the whole radio is likely to be unnecessarily high. Without downconversion, it is not just the ADC to run at RF speed, e.g. in the GHz range, but also the channel filter, the VGA, and the digital front-end. However, the desired signal protocol (channel) bandwidth is often on the order of 1000 times smaller, e.g. in the MHz range. A lower operating speed means a lower overall power consumption, both for active analog circuits such as amplifiers and filters (static power) and for switching circuits such as quantizers and digital gates (dynamic power). Without downconversion early in the receiver chain, the required power of the whole radio would be dramatically increased.

For mobile applications, the reduced power consumption is a key advantage of applying downconversion early in a receiver, although the resulted architecture might not be as flexible as the ideal software-radio receiver (see Section 1.1).

Other than in receivers, frequency translation blocks are also widely applied in transmitters (Fig. 2.1), for either downconversion or upconversion. They usually share a similar motivation as for receivers, i.e. to make functions such as AD/DA conversion and phase detection feasible and to reduce the power consumption of the entire system.

This thesis mainly focuses on the receiver side, mostly involving frequency downconversion which is also the main subject of the rest of this chapter. Nevertheless, upconversion can be regarded as a counterpart, sharing most of the discussed principles.

| Input Principle | Analog-CT              | Analog-DT                         | Digital                        |

|-----------------|------------------------|-----------------------------------|--------------------------------|

|                 | (CT CA)                | (DT CA)                           | (DT DA)                        |

| Mixing          | CT Mixing <sup>1</sup> | DT Mixing <sup>2</sup> (proposed) | Digital<br>Mixing <sup>3</sup> |

| Sampling        | CT-to-DT               | DT Re-                            | Digital Re-                    |

|                 | Sampling²              | sampling <sup>2</sup>             | sampling³                      |

<sup>1</sup>RF-mixing receiver <sup>2</sup>RF-sampling receiver <sup>3</sup>Ideal SWR receiver

Table 2.1 Classification of frequency downconversion techniques based on the type of input signal and the downconversion principle

Different frequency downconversion techniques have been proposed for radio receivers, most notably mixing and sampling. We would like to compare them and answer questions such as: what are the fundamental distinctions among them, is it really more flexible to sample as early as possible in a receiver chain, and does sampling suffer more from clock jitter compared to mixing?

In order to clarify the differences among downconversion techniques, we first propose a classification of them.

## 2.2 Classification of Downconversion Techniques

Table 2.1 classifies various downconversion techniques based on two aspects. The columns are defined by the input signal domain, i.e. continuous-time (CT) versus discrete-time and continuous-amplitude versus discrete-amplitude <sup>2</sup>. The rows distinguish in downconversion principle, i.e. mixing or sampling<sup>3</sup>.

\_

<sup>&</sup>lt;sup>2</sup> A column for continuous-time discrete-amplitude signal can also be added, but we omitted it because we are not aware of any practical radio examples yet operating in this domain, although some work [8] [9] tried to explore the potential benefits of CT DSP systems. Such type of signal often appears at the output of a digital-to-analog converter before applying a reconstruction filter.

<sup>&</sup>lt;sup>3</sup> Please note that sampling always provides a DT output, and hence it provides CT to DT conversion in case of a CT input, while under certain conditions as will be described in Section 2.3.2, it can also provide frequency translation.

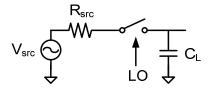

Figure 2.3 A general switching system for mixer or sampler

There are two techniques to achieve downconversion for each type of input signal:

- 1) For an analog-CT input signal, which is continuous in both time and amplitude, the downconversion can be realized via either CT mixing or CT-to-DT sampling.

- 2) For an analog-DT input signal, which is discrete in time but continuous in amplitude, DT mixing is possible. Alternatively, DT re-sampling can realize frequency conversion, also called decimation for down-sampling which reduces the sample rate.

- 3) For a digital input signal, which is discrete in both time and amplitude, downconversion can be done by digital mixing or digital re-sampling.

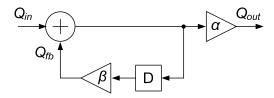

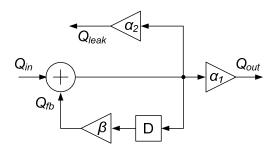

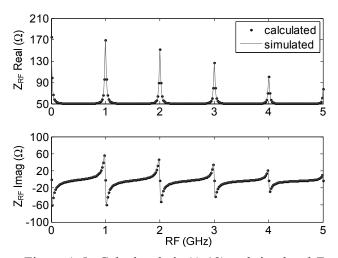

In Table 2.1, while all the other five techniques have been discussed in literature, to the authors' knowledge, we were the first to propose and implement the concept of DT mixing [10].